Computer Science > QUESTIONS & ANSWERS > Questions and Answers > DEE EE3043 KTMT (All)

Questions and Answers > DEE EE3043 KTMT

Document Content and Description Below

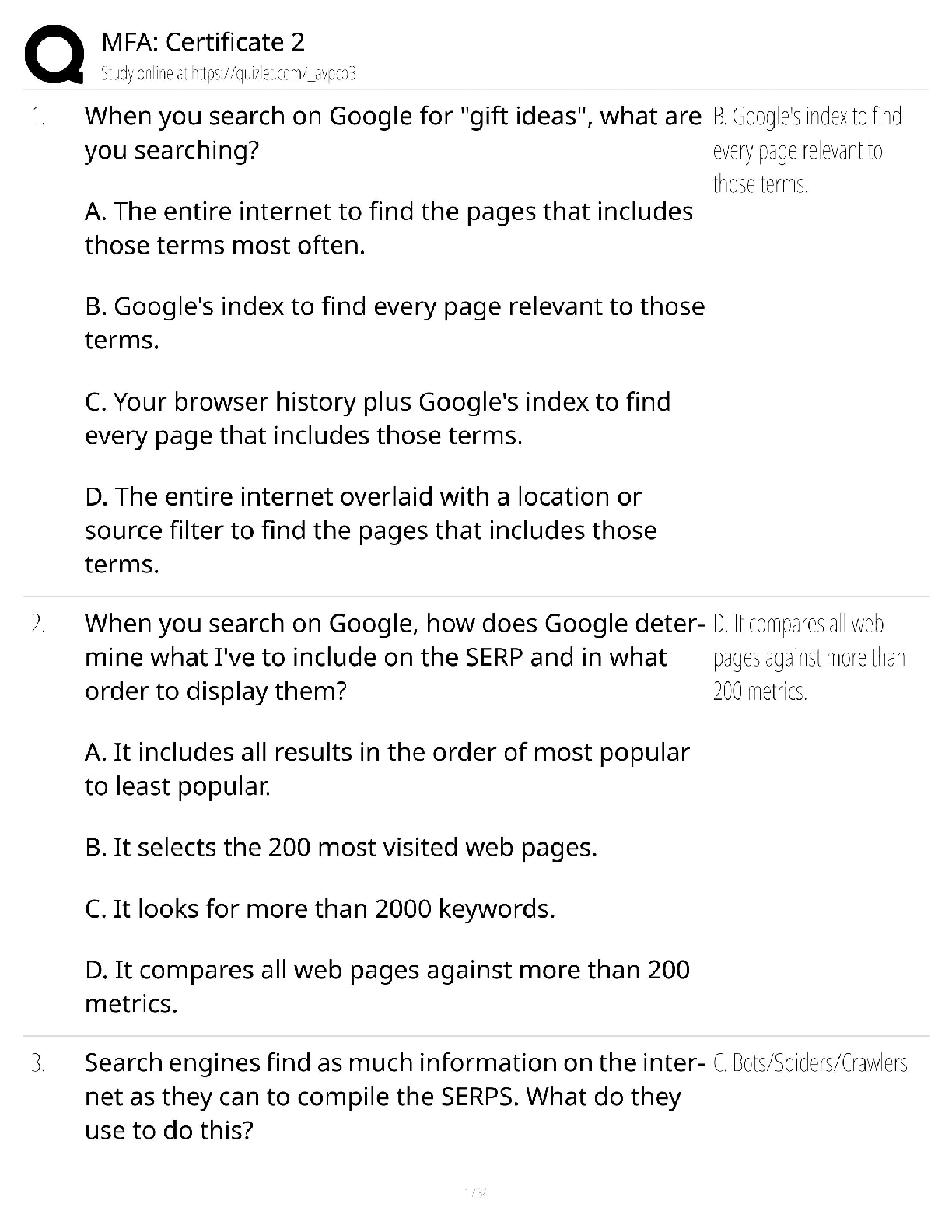

DEE EE3043KTMT A memory chip has 12 address pins, determine the maximum memory words of this chip? Select one: 4096 2048K 2048 4000 To balance the super speed of CPU with the slow response ... of memory, which of the following measures have been made by engineers in system design? Select one or more: Using higher-speed bus and us hierarchy Make use of both on-chip and off-chip cache memory Make wider data bus path To move data directly by DMA Basic functions that a computer can perform including: Select one or more: Control Data processing Direct memory access Data movement Data storage Interrupt What are the features of direct-mapping cache organization? Select one or more: Thrash --> low hit ratio faster small cache memory Simple and inexpensive Calculate the CPI for this program The formula to calculate CPI: CPI = CPU time / I Answer: In computer organization, the CPU transfer rate is much higher than that of memory. It is easy to match performance of these components by: Select one: increase the bus speed producing faster memory module Introducing cache memory increase I/O speed What is correct about the function of TRIM command in SSD? Select one: Allow SSD to manage occupied pages and remove them automatically for later use Allow OS to notify SSD the presence of occupied blocks of data which are no longer in use and can be erased internally Allow SSD to allocate memory pages in blocks properly for faster access Allow SSD to defragment scattered data stored in separate pages Which one best describe cache hit and cache miss? | Cache hit ratio | Answer 1 Chọn... the number of memory accesses that the CPU can retrieve from the cache per the total number of memory accesses the number of memory accesses that CPU must retrieve from the main memory per the total number of memory accesses the number of memory accesses that hit the cache per the total access | Cache miss ratio | Answer 2 Chọn... the number of memory accesses that the CPU can retrieve from the cache per the total number of memory accesses the number of memory accesses that CPU must retrieve from the main memory per the total number of memory accesses the number of memory accesses that hit the cache per the total access Key parameters to consider when evaluating processor hardware include: Select one or more: reliability size Address bus size performance power consumption databus size cost Match correct definitions of Computer Organization and Architecture | Computer Architecture refers to Answer 1 Chọn... attribute of the system visible to a programmer such as instruction set, bits, bytes... Interconnection among computer module such as processor, IO, memory... Operational units and their interconnections including hardware details such as control signals, interfaces with peripherals or memory technology Computer Organization refers to | Answer 2 Chọn... attribute of the system visible to a programmer such as instruction set, bits, bytes... Interconnection among computer module such as processor, IO, memory... Operational units and their interconnections including hardware details such as control signals, interfaces with peripherals or memory technology A processor with 16-bit instruction set. The instruction composed of 2 fields: the first byte contains the opcode and the remainder the operand or an operand address. What is the maximum directly addressable memory capacity? Select one: 256K 256 1024 512 As a consequence of Moore's law: the number of transistors on a single chip continues to grow year by year. Together with the increasing clock speed to increase the performance, power consumption in processor chips rises fast. What design engineers had made to increase processor performance but still keep the heat dissipation at a proper level. Select one: produce multicore processor chip make wider data bus to increase the bandwidth between processor and main memory produce on-chip and off-chip cache memory lower internal clock speed of CPU When many devices of different transmission speed connect to the same bus, the overall system performance suffers. How did the design engineers resolved this: Select one: PCI Express bus Multiple-Bus hierarchies PCI bus Split system bus into local bus and memory bus Consider a magnetic disk drive with 8 surfaces, 512 tracks per surface, and 64 sectors per track. Sector size is 1 kB. What is the disk capacity Answer: Select one unit Chọn... MB KB A SRAM memory chip labeled 32x8bit. Which of the following is correct pinout regarding address and data lines? Select one: 32 address pins, 4 data pins 15 address pins, 8 data pins 5 address pins, 3 data pins 32 address pins, 3 data pins Choose correct features for SRAM and DRAM | DRAM | Answer 1 Chọn... Faster access time, cheaper cost per bit, can manufacture with larger size Slower access time, cheaper cost per bit, can manufacture with larger size Slow access time, cheaper cost per bit, can only manufacture at larger size Faster access time, cost more per bit, smaller size | SRAM | Answer 2 Chọn... Faster access time, cheaper cost per bit, can manufacture with larger size Slower access time, cheaper cost per bit, can manufacture with larger size Slow access time, cheaper cost per bit, can only manufacture at larger size Faster access time, cost more per bit, smaller size For cache write policies, which are often used for write-hit and write-miss | Write-miss | Answer 1 Chọn... Write-allocate Write-no-allocate Write-back Write-through | Write-hit | Answer 2 Chọn... Write-allocate Write-no-allocate Write-back Write-through What can be concluded from the following chart xxxxxxxxxxxxxxxxxxxxxxx Select one or more: The speedup is significant when move to several cores and inherently serial code is small. When the parallelizable code is small, the speedup made is insignificant. When the inherently serial code is large, the improvement made is significant. Speedup is the same when the parallelizable code equally comparable to serial one. Major structural components of the CPU include: Select one or more: Control Unit Interconnections Instruction Register Instruction Pointer (PC) Registers Arithmetic and Logic Unit Select correct level for contemporary computer multilevel machine | Level 0 | Answer 1 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Level 5 | Answer 2 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Level 2 | Answer 3 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Layer 4 | Answer 4 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Level 1 | Answer 5 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Level 6 | Answer 6 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level | Level 3 | Answer 7 Chọn... Internet Microarchitecture level Applications Instruction set level Digital logic level High level programming language Assembly Language level Operating system level Consider a 16-bit microprocessor, with a 16-bit external data bus, driven by an 10-MHz input clock. Assume that this microprocessor has a bus cycle whose minimum duration equals four input clock cycles. What is the maximum data transfer rate across the bus that this microprocessor can sustain? Select one: 10 MB/s 1 MB/s 4 MB/s 5 MB/s Which ones are not correct for static RAM? Select one or more: Cost per bit is higher than dynamic RAM Cost per bit is lower than dynamic RAM faster than dynamic RAM because they are made from capacitor Cheaper than dynamic RAM because simpler chip controller In the interconnection system, the number of address lines are governs by Select one: CPU data bus line I/O Module Memory size What is the correct sequence of instruction cycle? | Step 2 | Answer 1 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution | Step 6 | Answer 2 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution | Step 1 | Answer 3 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution | Step 5 | Answer 4 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution | Step 4 | Answer 5 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution | Step 3 | Answer 6 Chọn... Store result Fetch opcode Calculate operand address Fetch operand Decode Execution For memory hierarchy below, which relationship hold when moving downward xxxxxxxxxxxxxxxxxxxx Select one or more: the processor accesses more often Decreasing cost per bit Increasing capacity Decreasing frequency of access by the processor Increasing access time Which of the following best describe the memory chip with pinout as shown below: xxxxxxxxxxxxxxxx DQ: Data pinout Select one: SRAM 256Kx1-bit SDRAM 64Kx4-bit DRAM 64Kx4-bit DRAM 16Kx4-bit Which is correct about dual-layer DVD? Select one: contains layers on both sides of the disk for writing data to the same as double-sided DVD contains two layers on a single side for writing data to DVD drives has double laser head for reading from or writing to this disk What can be concluded from the following chart of processor trends: xxxxxxxxxxxxxxxxxxx Select one: Heat dissipation in processor chip is increasing year after year since 1970 The processor speed keeps increasing after 2003 The number of transistors in chips produce more heat dissipation The multi-core processors and level off clock speed help to make heat dissipation of CPU chip less Which statements are correct for HDDs? Select one or more: a. Bits are stored on tracks b. Head, Track, Sector are key parameters for access data on hard disk c. Bits are store randomly on disk surfaces d. Head, Track, Cylinder are key parameters for access data on hard disk Structural components of computer include: Select one or more: Central processing unit DMA System interconnection I/O Interrupt Memory Which is not correct about MOORE's law? Select one or more: The number of transistors that could be put on a single chip was doubling every year except 1970s Likely triple after 2000 The number of transistors that could be put on a single chip was doubling every year The number of transistors that could be put on a single chip was triple every year nowadays. Identify the correct sequence to update a page onto a flash memory? | Step 2 | Answer 1 Chọn... the entire page is read from flash into RAM then request data in page is update The entire block from RAM then is written back to the flash memory the entire block of flash memory are erased the entire block is being read from flash into RAM then request data in page is update | Step 1 | Answer 2 Chọn... the entire page is read from flash into RAM then request data in page is update The entire block from RAM then is written back to the flash memory the entire block of flash memory are erased the entire block is being read from flash into RAM then request data in page is update | Step 3 | Answer 3 Chọn... the entire page is read from flash into RAM then request data in page is update The entire block from RAM then is written back to the flash memory the entire block of flash memory are erased the entire block is being read from flash into RAM then request data in page is update To evaluate processor performance, the following indicators and formulas are used: xxxxxxxxxxxxxxxxxxxxx Which of the following system attributes affects Ic (the number of instructions of a program) Select one or more: Instruction set architecture Processor implementation Compiler technology Cache and memory hierarchy Calculate the execution time for this program. Given: xxxxxxxxxxxxxxxxxxxxxxxxx Answer: [Show More]

Last updated: 3 years ago

Preview 1 out of 9 pages

Buy this document to get the full access instantly

Instant Download Access after purchase

Buy NowInstant download

We Accept:

Reviews( 0 )

$12.00

Can't find what you want? Try our AI powered Search

Document information

Connected school, study & course

About the document

Uploaded On

Jan 10, 2021

Number of pages

9

Written in

All

Additional information

This document has been written for:

Uploaded

Jan 10, 2021

Downloads

0

Views

149

.png)

.png)

.png)

.png)

.png)

.png)

.png)